# FLEX I/O Isolated Analog Modules

1794-IF4I, -OF4I, IF2XOF2I, -IF4IXT, -IF4ICFXT, -OF4IXT, IF2XOF2IXT

**User Manual**

Rockwell Automation

## **Important User Information**

Solid state equipment has operational characteristics differing from those of electromechanical equipment. Safety Guidelines for the Application, Installation and Maintenance of Solid State Controls (publication SGI-1.1 available from your local Rockwell Automation sales office or online at <a href="http://literature.rockwellautomation.com">http://literature.rockwellautomation.com</a>) describes some important differences between solid state equipment and hard-wired electromechanical devices. Because of this difference, and also because of the wide variety of uses for solid state equipment, all persons responsible for applying this equipment must satisfy themselves that each intended application of this equipment is acceptable.

In no event will Rockwell Automation, Inc. be responsible or liable for indirect or consequential damages resulting from the use or application of this equipment.

The examples and diagrams in this manual are included solely for illustrative purposes. Because of the many variables and requirements associated with any particular installation, Rockwell Automation, Inc. cannot assume responsibility or liability for actual use based on the examples and diagrams.

No patent liability is assumed by Rockwell Automation, Inc. with respect to use of information, circuits, equipment, or software described in this manual.

Reproduction of the contents of this manual, in whole or in part, without written permission of Rockwell Automation, Inc., is prohibited.

Throughout this manual, when necessary, we use notes to make you aware of safety considerations.S

#### WARNING

Identifies information about practices or circumstances that can cause an explosion in a hazardous environment, which may lead to personal injury or death, property damage, or economic loss.

#### **IMPORTANT**

Identifies information that is critical for successful application and understanding of the product.

#### **ATTENTION**

Identifies information about practices or circumstances that can lead to: personal injury or death, property damage, or economic loss. Attentions help you identify a hazard, avoid a hazard, and recognize the consequence.

#### **SHOCK HAZARD**

Labels may be on or inside the equipment, such as a drive or motor, to alert people that dangerous voltage may be present.

#### **BURN HAZARD**

Labels may be on or inside the equipment, such as a drive or motor, to alert people that surfaces may reach dangerous temperatures.

Rockwell Automation, Allen-Bradley, FLEX, RSNetWorx, RSLogix5000, and TechConnect are trademarks of Rockwell Automation, Inc.

Trademarks not belonging to Rockwell Automation are property of their respective companies.

## **Using this Manual**

## **Purpose of this Manual**

This manual shows you how to use your FLEX I/O Isolated Analog modules with Allen-Bradley programmable controllers. The manual helps you install, program and troubleshoot your modules.

Except where noted, information that applies to 1794-IF4I, 1794-OF4I, and IF2XOF2I also applies to 1794-IF4IXT, 1794-IF4ICFXT, 1794-OF4IXT, and IF2XOF2IXT.

#### **Audience**

You must be able to program and operate an Allen-Bradley programmable controller to make efficient use of your FLEX I/O modules. In particular, you must know how to program block transfers.

We assume that you know how to do this in this manual. If you do not, refer to the appropriate programming and operations manual before you attempt to program your modules.

## **Vocabulary**

In this manual, we refer to:

- the isolated analog input or isolated analog output module as the "input module" or "output module"

- the Programmable Controller as the "controller"

## **Manual Organization**

This manual is divided into five chapters. The following chart lists each chapter with its corresponding title and a brief overview of the topics covered in that chapter.

| Section   | Title                                                                  | Contents                                                                          |  |  |

|-----------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Chapter 1 | Overview of FLEX I/O and your Analog Modules                           | Describes FLEX I/O Isolated<br>Analog modules, features,<br>and how they function |  |  |

| Chapter 2 | How to Install Your Analog<br>Module                                   | How to install and wire the modules                                               |  |  |

| Chapter 3 | Module Programming Explains block transfi programming, sample programs |                                                                                   |  |  |

| Section    | Title                                                                                               | Contents                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Chapter 4  | Writing Configuration to and<br>Reading Status from Your<br>Module with a Remote I/O<br>Adapter     | Explains how to configure your modules and read status information from your modules when using a remote I/O adapter |

| Chapter 5  | Communication and I/O<br>Image Table Mapping with<br>the DeviceNet/ControlNet<br>Adapter            | Explains how you communicate with your modules, and how the I/O image is mapped when using a DeviceNet adapter       |

| Chapter 6  | Input, Output, Status and<br>Configuration Files for<br>Analog Modules when used<br>with ControlNet | Explains how you communicate with your modules over ControlNet.                                                      |

| Chapter 7  | Calibrating Your Module                                                                             | Explains how to calibrate your module.                                                                               |

| Appendix A | Specifications                                                                                      | Specifications for the isolated analog modules                                                                       |

| Appendix B | Class I, Division 2, Group A,<br>B, C, D Hazardous Locations<br>Statement                           | Hazardous location approval                                                                                          |

## Common Techniques Used in this Manual

The following conventions are used throughout this manual:

- Bulleted lists such as this one provide information, not procedural steps.

- Numbered lists provide sequential steps or hierarchical information.

## **For Additional Information**

For additional information on FLEX I/O systems and modules, refer to the following documents:

| Catalog Numbers | Voltage | Description                        | Publications                 |             |

|-----------------|---------|------------------------------------|------------------------------|-------------|

|                 |         |                                    | Installation<br>Instructions | User Manual |

| 1794            |         | 1794 FLEX I/O Product Data         | 1794-2.1                     |             |

| 1794-ACN        | 24V dc  | ControlNet Adapter                 | 1794-5.8                     |             |

| 1794-ACNR       | 24V dc  | Redundant Media ControlNet Adapter | 1794-5.18                    |             |

| 1794-ADN        | 24V dc  | DeviceNet Adapter                  | 1794-5.14                    | 1794-6.5.5  |

| 1794-ASB/C      | 24V dc  | Remote I/O Adapter                 | 1794-5.46                    | 1794-6.5.9  |

| Catalog Numbers      | Voltage | Description                                    | Publications                 |             |

|----------------------|---------|------------------------------------------------|------------------------------|-------------|

|                      |         |                                                | Installation<br>Instructions | User Manual |

| 1794-ASB2            | 24V dc  | 2-Slot Remote I/O Adapter                      | 1794-5.44                    | 1794-6.5.3  |

| 1794-TB2<br>1794-TB3 |         | 2-wire Terminal Base<br>3-wire Terminal Base   | 1794-5.2                     |             |

| 1794-TBN             |         | Terminal Base Unit                             | 1794-5.16                    |             |

| 1794-TBNF            |         | Fused Terminal Base Unit                       | 1794-5.17                    |             |

| 1794-TB3T            |         | Temperature Terminal Base Unit                 | 1794-5.41                    |             |

| 1794-TB3S            |         | Spring Clamp Terminal Base Unit                | 1794-5.42                    |             |

| 1794-TB3TS           |         | Spring Clamp Temperature Terminal Base<br>Unit | 1794-5.43                    |             |

| 1794-IB16            | 24V dc  | 16 Sink Input Module                           | 1794-5.4                     |             |

| 1794-OB16            | 24V dc  | 16 Source Output Module                        | 1794-5.3                     |             |

| 1794-IV16            | 24V dc  | 16 Source Input Module                         | 1794-5.28                    |             |

| 1794-0V16            | 24V dc  | 16 Sink Output Module                          | 1794-5.29                    |             |

| 1794-OB8EP           | 24V dc  | 8 Electronically Fused Output Module           | 1794-5.20                    |             |

| 1794-0W8             | 24V dc  | 8 Output Relay Module                          | 1794-5.19                    |             |

| 1794-IB10X0B6        | 24V dc  | 10 Input/6 Output Module                       | 1794-5.24                    |             |

| 1794-IE8             | 24V dc  | Selectable Analog 8 Input Module               | 1794-5.6                     |             |

| 1794-0E4             | 24V dc  | Selectable Analog 4 Output Module              | 1794-5.5                     | 1794-6.5.2  |

| 1794-IE4X0E2         | 24V dc  | 4 Input/2 Output Analog Module                 | 1794-5.15                    |             |

| 1794-IR8             | 24V dc  | 8 RTD Input Analog Module                      | 1794-5.22                    | 1794-6.5.4  |

| 1794-IT8             | 24V dc  | 8 Thermocouple Input Module                    | 1794-5.21                    | 1794-6.5.7  |

| 1794-IB8S            | 24V dc  | Sensor Input Module                            | 1794-5.7                     |             |

| 1794-IA8             | 120V ac | 8 Input Module                                 | 1794-5.9                     | 7           |

| 1794-0A8             | 120V ac | Output Module                                  | 1794-5.10                    |             |

| 1794-CE1, -CE3       |         | Extender Cables                                | 1794-5.12                    |             |

| 1794-NM1             |         | Mounting Kit                                   | 1794-5.13                    |             |

| 1794-PS1             | 24V dc  | Power Supply                                   | 1794-5.35                    |             |

| 1794-PS13            | 24V dc  | Power Supply                                   | 1794-5.69                    |             |

## **Summary**

This preface gave you information on how to use this manual efficiently. The next chapter introduces you to the remote I/O adapter module.

## Table of Contents

|                               | Important User Information                               | . 2 |

|-------------------------------|----------------------------------------------------------|-----|

| Preface                       | Using this Manual                                        |     |

|                               | Purpose of this Manual                                   |     |

|                               | Audience                                                 |     |

|                               | Vocabulary                                               | . 3 |

|                               | Manual Organization                                      | . 3 |

|                               | Common Techniques Used in this Manual                    | . 4 |

|                               | For Additional Information                               | . 4 |

|                               | Summary                                                  | . 5 |

| Table of Contents             | Chapter                                                  |     |

| Overview of FLEX I/O and your | Chapter Objectives                                       | 11  |

| Analog Modules                | The FLEX I/O System                                      |     |

| Allulog Moutiles              | Types of FLEX I/O Modules                                |     |

|                               | How FLEX I/O Analog Modules Communicate with             |     |

|                               | Programmable Controllers                                 | 13  |

|                               | Features of Your Analog Modules                          |     |

|                               | Summary                                                  |     |

|                               | odiffically                                              |     |

|                               | Chapter                                                  |     |

| How to Install Your Analog    | •                                                        | 15  |

| •                             | Chapter Objectives                                       |     |

| Module                        | Before You Install Your Analog Module                    |     |

|                               | Compliance to European Union Directives                  |     |

|                               | EMC Directive                                            |     |

|                               | Low Voltage Directive (to be confirmed)                  |     |

|                               | Power Requirements                                       |     |

|                               | Installing the Module                                    |     |

|                               | Mounting the Terminal Base Unit on a DIN Rail            |     |

|                               | Panel/Wall Mounting                                      |     |

|                               | Mounting the Analog Module on the Terminal Base Unit.    |     |

|                               | Connecting Wiring for the Analog Modules                 |     |

|                               | Connecting Wiring using a 1794-TB3, -TB3T, -TB3S or -TB3 |     |

|                               | Terminal Base Unit                                       |     |

|                               | Wiring to a 1794-TBN or 1794-TBNF Terminal Base Unit.    |     |

|                               | Module Indicators                                        |     |

|                               | Chapter Summary                                          | 30  |

|                               | Chapter                                                  |     |

| Module Programming            | Chapter Objectives                                       | 21  |

| wiodule i rogramming          | Block Transfer Programming                               |     |

|                               |                                                          |     |

|                               | Configuration Rungs                                      |     |

|                               | Example Configuration Rungs                              |     |

|                               | Sample Programs for FLEX I/O Analog Modules              |     |

|                               | PLC-3 Programming                                        |     |

|                               | PLC-5 Programming                                        |     |

|                               | PLC-2 Programming                                        |     |

|                               | SLC-5 Programming                                        | 38  |

|                                                              | Chapter Summary                                                                                                              |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Writing Configuration to and Reading Status from Your Module | ChapterChapter Objectives53Configuring Your Analog Module53                                                                  |

| with a Remote I/O Adapter                                    | Range Selection54Safe State Selection54Data Format54Real Time Sampling55                                                     |

|                                                              | Input Filtering                                                                                                              |

|                                                              | Reading Data From Your Module                                                                                                |

|                                                              | 8 Input Analog Module (Cat. No. 1794-IF4I)                                                                                   |

|                                                              | 4 Isolated Output Analog Module (Cat. No. 1794-OF4I). 64<br>2 Input/2 Output Analog Combo Module (Cat. No.<br>1794-IF2XOF2I) |

|                                                              | Chapter Summary                                                                                                              |

|                                                              | Chapter                                                                                                                      |

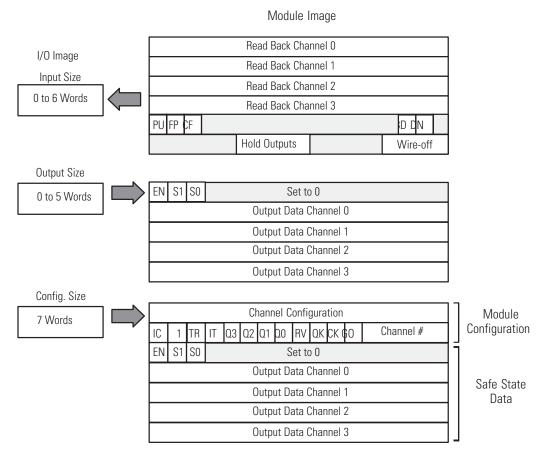

| Communication and I/O Image                                  | Chapter Objectives                                                                                                           |

| Table Mapping with the                                       | About RSNetWorx and RSLogix                                                                                                  |

| DeviceNet/ControlNet Adapter                                 | Polled I/O Structure                                                                                                         |

|                                                              | Mapping Data into the Image Table                                                                                            |

|                                                              | 4 Input Isolated Analog Module (Cat. No. 1794-IF4I) Image                                                                    |

|                                                              | Table Mapping                                                                                                                |

|                                                              | 4 Output Isolated Analog Module (Cat. No. 1794-OF4I) Image Table Mapping                                                     |

|                                                              | Series B) Image Table Mapping                                                                                                |

|                                                              | Defaults                                                                                                                     |

|                                                              | Chapter                                                                                                                      |

| Input, Output, Status and                                    | Chapter Objectives                                                                                                           |

| Configuration Files for Analog                               | About the ControlNet Adapter                                                                                                 |

| Modules when used with                                       | Commun ication Over the FLEX I/O Backplane                                                                                   |

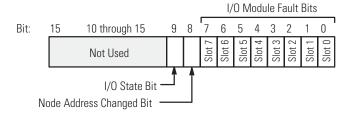

| ControlNet                                                   | Adapter Input Status Word                                                                                                    |

|                                                              | Safe State Data                                                                                                              |

|                                                              | Communication Fault Behavior                                                                                                 |

|                                                              | Idle State Behavior102Input Data Behavior Upon Module Removal103                                                             |

|                                                              | 4 Input Isolated Analog Module (Cat. No. 1794-IF4I) Image                                                                    |

|                                                              | Table Mapping                                                                                                                |

| Class I, Division 2, Group A, B, C, D<br>Hazardous Locations Statement | Appendix                                                           |

|------------------------------------------------------------------------|--------------------------------------------------------------------|

| Specifications                                                         | Appendix Filter Response for 150Hz, 300Hz and 600Hz Conversion 134 |

|                                                                        | Annondiv                                                           |

|                                                                        | Chapter Summary                                                    |

|                                                                        | Scaling Outputs                                                    |

|                                                                        | Scaling Inputs                                                     |

|                                                                        | Final Gain Calibration for Current Inputs 130                      |

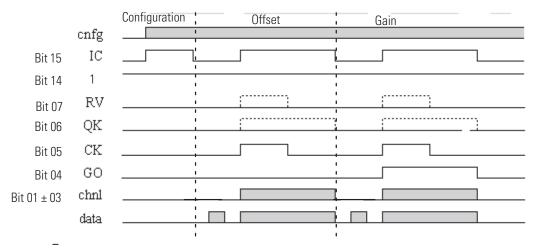

|                                                                        | Offset Calibration for Current Outputs 128                         |

|                                                                        | Calibrating Current Outputs                                        |

|                                                                        | Gain Calibration for Outputs 127                                   |

|                                                                        | Offset Calibration for Voltage Outputs 126                         |

|                                                                        | Calibrating Voltage Outputs                                        |

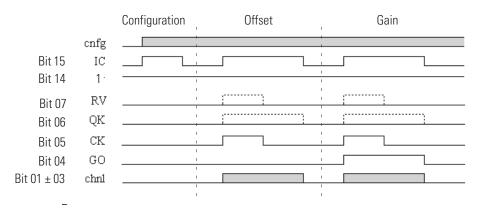

|                                                                        | Bits Used During Calibration                                       |

|                                                                        | Calibrating Your Isolated Analog Output Module 125                 |

|                                                                        | Setting the Input Gain                                             |

|                                                                        | Offset Calibration for Inputs                                      |

|                                                                        | Bits Used During Calibration                                       |

|                                                                        | Tools and Equipment                                                |

|                                                                        | When and How to Calibrate Your Isolated Analog Module . 119        |

| Calibrating Your Module                                                | Chapter Objective                                                  |

|                                                                        | Chapter                                                            |

|                                                                        | Image Table Mapping 113                                            |

|                                                                        | Isolated Analog Combo Module (Cat. No. 1794-IF2XOF2I)              |

|                                                                        | Table Mapping                                                      |

|                                                                        | 4 Output Isolated Analog Module (Cat. No. 1794-OF4I) Image         |

Index

## Overview of FLEX I/O and your Analog Modules

## **Chapter Objectives**

In this chapter, we tell you about:

- what the FLEX I/O system is and what it contains

- types of FLEX I/O analog modules

- how FLEX I/O analog modules communicate with programmable controllers

- the features of your analog modules

### The FLEX I/O System

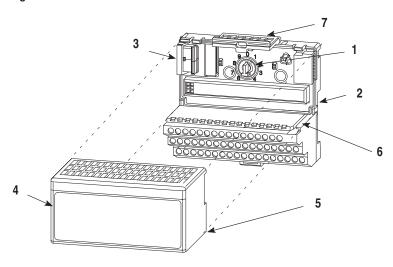

FLEX I/O is a small, modular I/O system for distributed applications that performs all of the functions of rack-based I/O. The FLEX I/O system contains the following components shown in Figure 1.1:

Figure 1.1

Adapter Terminal Base I/O Module

Allen-Bradley

Al

- adapter/power supply powers the internal logic for as many as eight I/O modules

- terminal base contains a terminal strip to terminate wiring for two- or three-wire devices

- I/O module contains the bus interface and circuitry needed to perform specific functions related to your application

## Types of FLEX I/O Modules

We describe the following FLEX I/O Analog modules in this user manual:

| Catalog Number | Voltage | Inputs | Outputs | Description                                       |

|----------------|---------|--------|---------|---------------------------------------------------|

| 1794-IF4I      | 24V dc  | 4      | -       | analog – 4 input, isolated                        |

| 1794-0F4I      | 24V dc  | _      | 4       | analog – 4 output, isolated                       |

| 1794-IF2X0F2I  | 24V dc  | 2      | 2       | analog – 2 input, isolated and 2 output, isolated |

FLEX I/O analog input, output and combination modules are block transfer modules that interface analog signals with any Allen-Bradley programmable controllers that have block transfer capability. Block transfer programming moves input from the module's memory to a designated area in the processor data table, and output data words from a designated area in the processor data table to the module's memory. Block transfer programming also moves configuration words from the processor data table to module memory.

The analog modules have selectable ranges as shown in the table below:

| Input Values | Data Format                | Underrange/Overrange        |  |  |

|--------------|----------------------------|-----------------------------|--|--|

| 4-20mA       | signed 2's complement      | 4% Underrange, 4% Overrange |  |  |

| ±10V         | signed 2's complement      | 2% Underrange, 2% Overrange |  |  |

| ±5V          | signed 2's complement      | 4% Underrange, 4% Overrange |  |  |

| 0-20mA       | signed 2's complement %    | 0% Underrange, 4% Overrange |  |  |

| 4-20mA       | signed 2's complement %    | 4% Underrange, 4% Overrange |  |  |

| 0-10V        | signed 2's complement %    | 0% Underrange, 2% Overrange |  |  |

| ±10V         | signed 2's complement %    | 2% Underrange, 2% Overrange |  |  |

| 0-20mA       | binary                     | 0% Underrange, 4% Overrange |  |  |

| 4-20mA       | binary                     | 4% Underrange, 4% Overrange |  |  |

| 0-10V        | binary                     | 0% Underrange, 2% Overrange |  |  |

| 0-5V         | binary                     | 0% Underrange, 4% Overrange |  |  |

| ±20mA        | offset binary, 8000H = 0mA | 4% Underrange, 4% Overrange |  |  |

| 4-20mA       | offset binary, 8000H = 4mA | 4% Underrange, 4% Overrange |  |  |

| ±10V         | offset binary, 8000H = 0V  | 2% Underrange, 2% Overrange |  |  |

| ±5V          | offset binary, 8000H = 0V  | 4% Underrange, 4% Overrange |  |  |

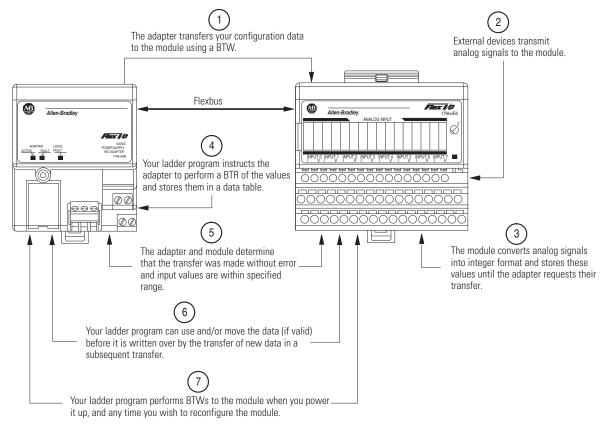

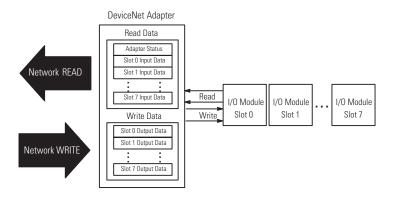

## How FLEX I/O Analog Modules Communicate with Programmable Controllers

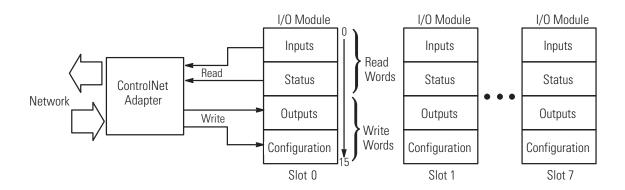

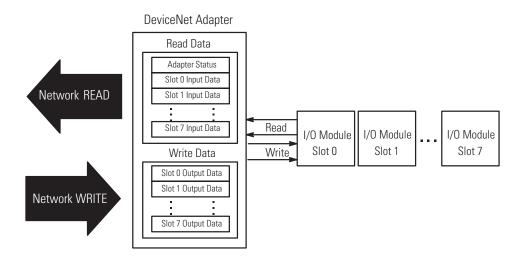

The adapter/power supply transfers data to the module (block transfer write) and from the module (block transfer read) using BTW and BTR instructions in your ladder diagram program. These instructions let the adapter obtain input values and status from the module, and let you send output values and establish the module's mode of operation. Figure 1.2 describes the communication process.

Figure 1.2

An Example of Communication Between an Adapter and an Analog Input Module

## Features of Your Analog Modules

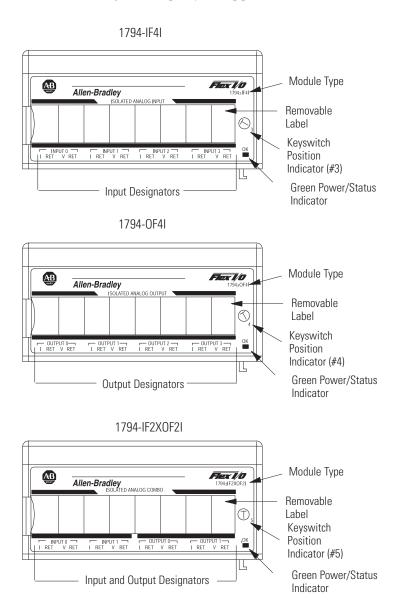

Each module has a unique label identifying its keyswitch position, wiring and module type. A removable label provides space for writing individual designations per your application.

## **Summary**

In this chapter you learned about the FLEX I/O system and the types of analog modules and how they communicate with programmable controllers.

## **How to Install Your Analog Module**

## **Chapter Objectives**

In this chapter, we tell you about:

- how to install your module

- how to set the module keyswitch

- how to wire the terminal base

- the indicators

## Before You Install Your Analog Module

Before installing your analog module in the I/O chassis:

| You need to:                                                     | As described under:                                                |

|------------------------------------------------------------------|--------------------------------------------------------------------|

| Calculate the power requirements of all modules in each chassis. | Power Requirements, page 2-16                                      |

| Position the keyswitch on the terminal base                      | Mounting the Analog Module on the<br>Terminal Base Unit, page 2-22 |

## Compliance to European Union Directives

If this product has the CE mark it is approved for installation within the European Union and EEA regions. It has been designed and tested to meet the following directives.

#### **EMC** Directive

This product is tested to meet Council Directive 2004/10/EC Electromagnetic Compatibility (EMC) and the following standards, in whole or in part, documented in a technical construction file:

- European Union 2004/108/EC EMC Directive, compliant with: EN 61326-1; Meas./Control/Lab., Industrial Requirements EN 61000-6-2; Industrial Immunity EN 61000-6-4; Industrial Emissions EN 61131-2; Programmable Controllers (Clause 8, Zone A & B)

- European Union 2006/95/EC LVD, compliant with: EN 61131-2; Programmable Controllers (Clause 11)

This product is intended for use in an industrial environment.

#### **Low Voltage Directive**

This product is tested to meet Council Directive 2006/95/EC Low Voltage, by applying the safety requirements of EN 61131–2 Programmable Controllers, Part 2 – Equipment Requirements and Tests.

For specific information required by EN 61131-2, see the appropriate sections in this publication, as well as the following Allen-Bradley publications:

- Industrial Automation Wiring and Grounding Guidelines For Noise Immunity, publication 1770-4.1

- Guidelines for Handling Lithium Batteries, publication AG-5.4

- Automation Systems Catalog, publication B111

Open style devices must be provided with environmental and safety protection by proper mounting in enclosures designed for specific application conditions. See NEMA Standards publication 250 and IEC publication 529, as applicable, for explanations of the degrees of protection provided by different types of enclosure.

## **Power Requirements**

The wiring of the terminal base unit is determined by the current draw through the terminal base. Make certain that the current draw does not exceed 10A.

Total current draw through the terminal base unit is limited to 10A. Separate power connections may be necessary.

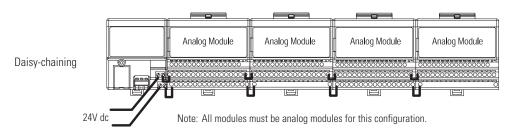

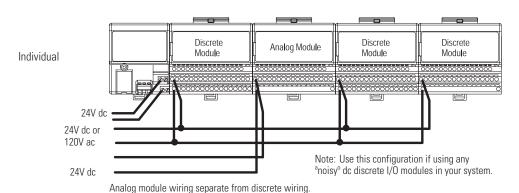

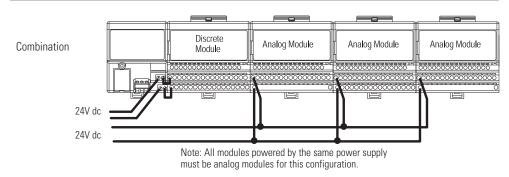

Methods of wiring the terminal base units are shown in the illustration below.

#### ATTENTION

Do not daisy chain power or ground from an analog terminal base unit to any ac or dc discrete module terminal base unit.

Wiring when total current draw is less than 10A

Wiring when total current draw is greater than 10A

Total current draw through any base unit must not be greater than 10A

## **Installing the Module**

Installation of the analog module consists of:

- mounting the terminal base unit

- installing the analog module into the terminal base unit

- installing the connecting wiring to the terminal base unit

If you are installing your module into a terminal base unit that is already installed, proceed to Mounting the Analog Module on the Terminal Base Unit on page 2-22.

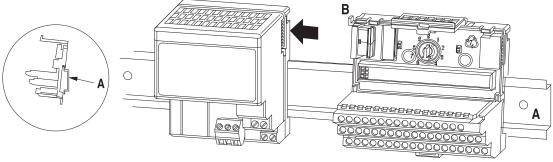

#### **Mounting the Terminal Base Unit on a DIN Rail**

ATTENTION

Do not remove or replace a terminal base unit when power is applied. Interruption of the flexbus can result in unintended operation or machine motion.

- **1.** Remove the cover plug (if used) in the male connector of the unit to which you are connecting this terminal base unit.

- **2.** Check to make sure that the 16 pins in the male connector on the adjacent device are straight and in line so that the mating female connector on this terminal base unit will mate correctly.

- **3.** Position the terminal base on the 35 x 7.5mm DIN rail **A** (A-B pt. no. 199-DR1; 46277-3; EN 50022) at a slight angle with hook **B** on the left side of the terminal base hooked into the right side of the unit on the left. Proceed as follows:

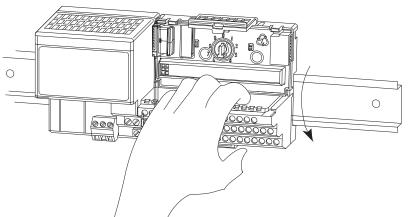

Figure 2.1

Position terminal base at a slight angle and hooked over the top of the DIN rail.

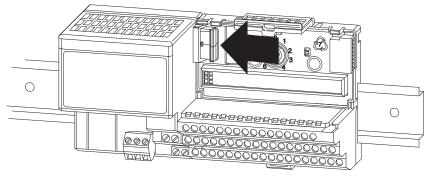

Figure 2.2

Slide the terminal base unit over tight against the adapter. Make sure the hook on the terminal base slides under the edge of the adapter and the flexbus connector is fully retracted.

Press down on the terminal base unit to lock the terminal base on the DIN rail. If the terminal base does not lock into place, use a screwdriver or similar device to open the locking tab, press down on the terminal base until flush with the DIN rail and release the locking tab to lock the base in place.

Gently push the flexbus connector into the side of the adapter to complete the backplane connection.

30077-M

**4.** Repeat steps 1 - 3 to install the next terminal base.

## **Panel/Wall Mounting**

Installation on a wall or panel consists of:

- $\bullet$  laying out the drilling points on the wall or panel

- drilling the pilot holes for the mounting screws

- mounting the adapter mounting plate

- installing the terminal base units and securing them to the wall or panel

If you are installing your module into a terminal base unit that is already installed, proceed to "Mounting the Analog Module on the Terminal Base" on .

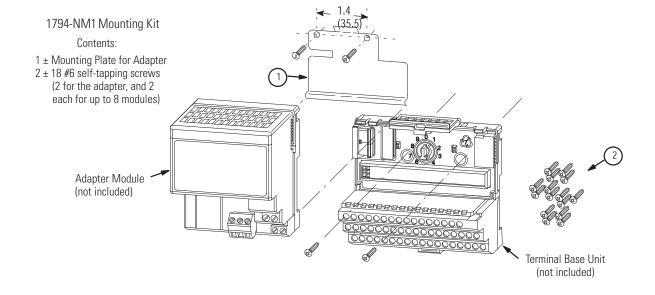

Use the mounting kit Cat. No. 1794-NM1 for panel/wall mounting.

To install the mounting plate on a wall or panel:

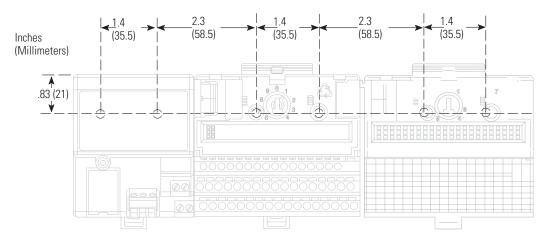

**1.** Lay out the required points on the wall/panel as shown in the drilling dimension drawing.

Figure 2.3 Drilling Dimensions for Panel/Wall Mounting of FLEX I/O

- **2.** Drill the necessary holes for the #6 self-tapping mounting screws.

- **3.** Mount the mounting plate (1) for the adapter module using two #6 self-tapping screws (18 included for mounting up to 8 modules and the adapter).

#### IMPORTANT

Make certain that the mounting plate is properly grounded to the panel. Refer to "Industrial Automation Wiring and Grounding Guidelines," publication 1770-4.1.

- **4.** Hold the adapter (2) at a slight angle and engage the top of the mounting plate in the indention on the rear of the adapter module.

- **5.** Press the adapter down flush with the panel until the locking lever locks.

- **6.** Position the terminal base unit up against the adapter and push the female bus connector into the adapter.

- 7. Secure to the wall with two #6 self-tapping screws.

- 8. Repeat for each remaining terminal base unit.

The adapter is capable of addressing eight modules. Do not exceed a maximum of eight terminal base units in your system.

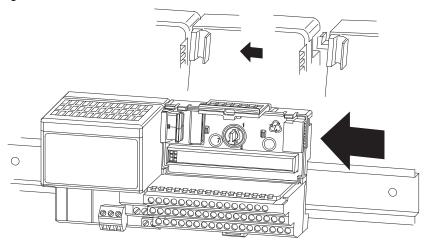

#### **Mounting the Analog Module on the Terminal Base Unit**

**1.** Rotate the keyswitch (1) on the terminal base unit (2) clockwise to the position required for the specific type of analog module.

Figure 2.4

| Analog Module Catalog Number          | Keyswitch Position |

|---------------------------------------|--------------------|

| 1794-IF4I, 1794-IF4IXT, 1794-IF4ICFXT | 3                  |

| 1794-0F4I, 1794-0F4IXT                | 4                  |

| 1794-IF2X0F2I, 1794-IF2X0F2IXT        | 5                  |

- Make certain the flexbus connector (3) is pushed all the way to the left to connect with the neighboring terminal base/adapter.

You cannot install the module unless the connector is fully extended.

- **3.** Make sure that the pins on the bottom of the module are straight so they will align properly with the connector in the terminal base unit.

- **4.** Position the module (4) with its alignment bar (5) aligned with the groove (6) on the terminal base.

- **5.** Press firmly and evenly to seat the module in the terminal base unit. The module is seated when the latching mechanism (7) is locked into the module.

**6.** Repeat the above steps to install the next module in its terminal base unit.

#### **ATTENTION**

Remove field-side power before removing or inserting the module. This module is designed so you can remove and insert it under backplane power. When you remove or insert a module with field-side power applied, an electrical arc may occur. An electrical arc can cause personal injury or property damage by:

- sending an erroneous signal to your system's field devices causing unintended machine motion

- causing an explosion in a hazardous environment

Repeated electrical arcing causes excessive wear to contacts on both the module and its mating connector. Worn contacts may create electrical resistance.

## Connecting Wiring for the Analog Modules

Wiring to the analog modules is made through the terminal base unit on which the module mounts.

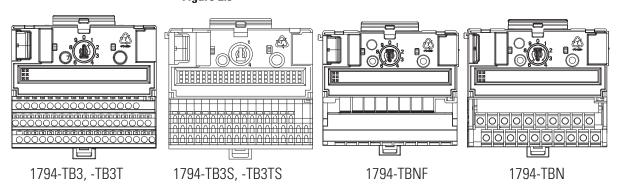

Refer to the following table for recommended terminal base units that you can use for each module.

| Module                                   | 1794-TB3 | 1794-TBT | 1794-TB3S | 1794-TB3TS | 1794-TB3S | 1794-TBN,<br>-TBNF |

|------------------------------------------|----------|----------|-----------|------------|-----------|--------------------|

| 1794-IF4I, 1794-IF4IXT,<br>1794-IF4ICFXT | Yes      | Yes      | Yes       | Yes        | Yes       | Yes                |

| 1794-0F4I, 1794-0F4IXT                   | Yes      | Yes      | Yes       | Yes        | Yes       | Yes                |

| 1794-IF2X0F2I,<br>1794-IF2X0F2IXT        | Yes      | Yes      | Yes       | Yes        | Yes       | Yes                |

Figure 2.5

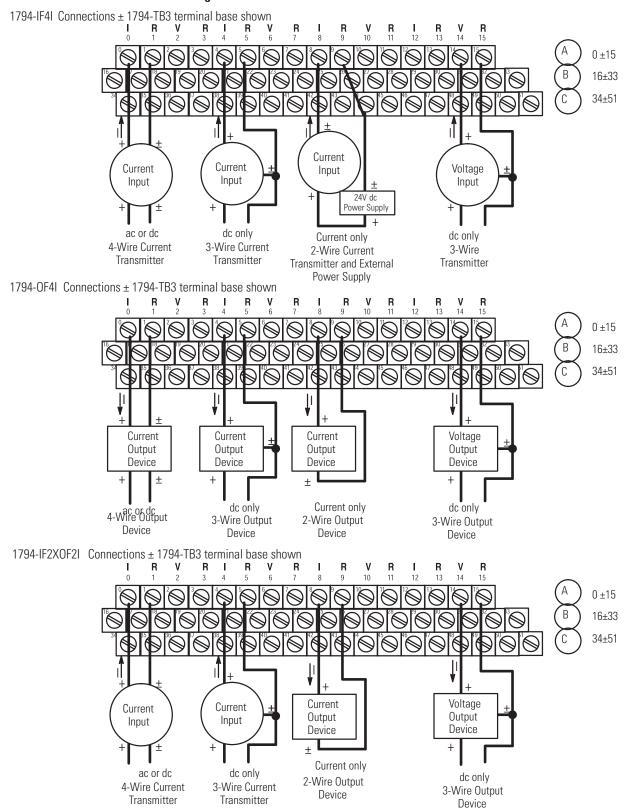

Connecting wiring for the individual analog modules is shown on:

| Module                                | Connecting Wiring |

|---------------------------------------|-------------------|

| 1794-IF4I, 1794-IF4IXT, 1794-IF4ICFXT | page 2-26         |

| 1794-0F4I, 1794-0F4IXT                |                   |

| 1794-IF2X0F2I, 1794-IF2X0F2IXT        | page 2-27         |

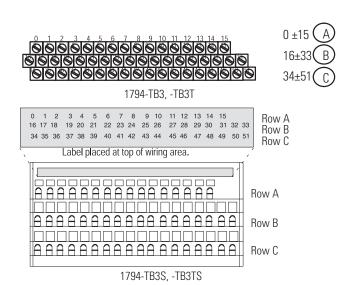

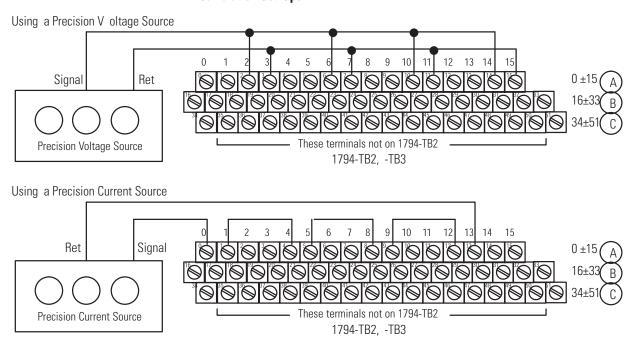

## Connecting Wiring using a 1794-TB3, -TB3T, -TB3S or -TB3TS Terminal Base Unit

1. Connect the individual signal wiring to numbered terminals on the 0–15 row (A) on the terminal base unit. (Use Belden 8761 cable for signal wiring.)

#### **ATTENTION**

Connect only one current or one voltage signal per channel. Do not connect both current and voltage on one channel.

2. Connect each channel signal return to:

1794-IF4I – the associated terminal on row A.

1794-OF4I – the corresponding terminal on the same row (A)

1794-IF4XOF2I – inputs – the associated terminal on row **A**; outputs – the corresponding terminal on the same row **(A)**.

**3.** Refer to Table 2.1 or Table 2.2. Connect +24V dc to designated terminals on the **34-51** row **(C)**, and 24V common todesignated terminals on the **16–33** row **(B)**.

#### ATTENTION

To reduce susceptibility to noise, power analog modules and discrete modules from separate power supplies. Do not exceed a length of 33 ft (10m) for dc power cabling.

#### **ATTENTION**

Remove field-side power before removing or inserting the module. This module is designed so you can remove and insert it under backplane power. When you remove or insert a module with field-side power applied, an electrical arc may occur. An electrical arc can cause personal injury or property damage by:

- sending an erroneous signal to your system's field devices causing unintended machine motion

- causing an explosion in a hazardous environment

Repeated electrical arcing causes excessive wear to contacts on both the module and its mating connector. Worn contacts may create electrical resistance.

**4.** If daisy chaining the +24V dc power to the next base unit, connect a jumper from terminal 51 on this base unit to terminal 34 on the next base unit. Connect the 24V dc common/return from terminal 33 on this base unit to terminal 16 on the next base unit.

### Wiring to a 1794-TBN or 1794-TBNF Terminal Base Unit

- 1. Connect individual input or output wiring to the even numbered terminals on row (B) as indicated in the table below.

- **2.** Connect the associated return wiring to the corresponding odd numbered terminal on row (C) for each input or output as indicated in the table below.

- **3.** Connect 24V dc to terminal 34 on row **(C)**.

- **4.** Connect 24V dc common to terminal 16 on row **(B)**.

- **5.** If continuing power to the next terminal base unit, connect a jumper from terminal 51 (24V dc) on this base unit to terminal 34 on the next base unit.

If continuing common to the next terminal base unit, connect a jumper from terminal 33 (24V dc common) on this base unit to terminal 16 on the next base unit.

Table 2.1

Wiring connections for 1794-TB3, -TB3T, -TB3S, -TB3TS, -TBN and -TBNF Terminal Base

Units when using the 1794-IF4I or 1794-OF4I Isolated Analog Module

| Channel | Signal Type | Label Markings | 1794-TB3, -TB3T1, -TB3S, -TB3TS <sup>(2)</sup><br>1794-TBN, 1794-TBNF |               |

|---------|-------------|----------------|-----------------------------------------------------------------------|---------------|

|         |             |                | Signal<br>Terminal                                                    | Signal Return |

| 0       | Current     | 10             | 0                                                                     |               |

|         | Current     | I0 Ret         |                                                                       | 1             |

|         | Voltage     | V0             | 2                                                                     |               |

|         | Voltage     | V0 Ret         |                                                                       | 3             |

| 1       | Current     | l1             | 4                                                                     |               |

|         | Current     | I1 Ret         |                                                                       | 5             |

|         | Voltage     | V1             | 6                                                                     |               |

|         | Voltage     | V1 Ret         |                                                                       | 7             |

Table 2.1

Wiring connections for 1794-TB3, -TB3T, -TB3TS, -TBN and -TBNF Terminal Base

Units when using the 1794-IF4I or 1794-OF4I Isolated Analog Module

| Channel Signal | Signal Type   | l Type Label Markings                                                                                    | 1794-TB3, -TB3T1, -TB3S, -TB3TS <sup>(2)</sup><br>1794-TBN, 1794-TBNF |               |

|----------------|---------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|

|                |               |                                                                                                          | Signal<br>Terminal                                                    | Signal Return |

| 2              | Current       | 12                                                                                                       | 8                                                                     |               |

|                | Current       | I2 Ret                                                                                                   |                                                                       | 9             |

|                | Voltage       | V2                                                                                                       | 10                                                                    |               |

|                | Voltage       | V2 Ret                                                                                                   |                                                                       | 11            |

| 3              | Current       | 13                                                                                                       | 12                                                                    |               |

|                | Current       | I3 Ret                                                                                                   |                                                                       | 13            |

|                | Voltage       | V3                                                                                                       | 14                                                                    |               |

|                | Voltage       | V3 Ret                                                                                                   |                                                                       | 15            |

|                | 24V dc Common | 1794-TB3 - 16 through 33 <sup>(1)</sup><br>1794-TB3T, -TB3TS - 17, 18, 33<br>1794-TBN, -TBNF - 16 and 33 |                                                                       | , 18, 33      |

|                | +24V dc power | 1794-TB3 — 34 thru 51<br>1794-TB3T, -TB3TS — 34, 35, 50, 51<br>1794-TBN, -TBNF — 34 and 51               |                                                                       |               |

$<sup>^{(1)}</sup>$  Terminals 16 thru 33 are internally connected in the terminal base unit.

Table 2.2 Wiring connections for the 1794-IF2XOF2I Isolated Analog Module when using 1794-TB3, -TB3T, -TB3TS, -TBN and -TBNF Terminal Base Units

| Channel | Signal Type | Label Markings | 1794-TB3, -TB3T <sup>(2)</sup> , -TB3S,<br>-TB3TS <sup>(2)</sup> -TBN, -TBNF |               |

|---------|-------------|----------------|------------------------------------------------------------------------------|---------------|

|         |             |                | Signal<br>Terminal                                                           | Signal Return |

| Input 0 | Current     | 10             | 0                                                                            |               |

|         | Current     | IO Ret         |                                                                              | 1             |

|         | Voltage     | V0             | 2                                                                            |               |

|         | Voltage     | V0 Ret         |                                                                              | 3             |

| Input 1 | Current     | I1             | 4                                                                            |               |

|         | Current     | I1 Ret         |                                                                              | 5             |

|         | Voltage     | V1             | 6                                                                            |               |

|         | Voltage     | V1 Ret         |                                                                              | 7             |

<sup>(2)</sup> Terminal 39 through 46 are chassis ground. Terminals 36, 37, 38 and 47, 48, 49 are used or cold junction compensation.

Table 2.2

Wiring connections for the 1794-IF2XOF2I Isolated Analog Module when using 1794-TB3,

-TB3T, -TB3TS, -TBN and -TBNF Terminal Base Units

| Channel  | Signal Type   | Label Markings | 1794-TB3, -TB3T <sup>(2)</sup> , -TB3S,<br>-TB3TS <sup>(2)</sup> -TBN, -TBNF                                                                                                          |               |  |

|----------|---------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

|          |               |                | Signal<br>Terminal                                                                                                                                                                    | Signal Return |  |

| Output 0 | Current       | I2             | 8                                                                                                                                                                                     |               |  |

|          | Current       | I2 Ret         |                                                                                                                                                                                       | 9             |  |

|          | Voltage       | V2             | 10                                                                                                                                                                                    |               |  |

|          | Voltage       | V2 Ret         |                                                                                                                                                                                       | 11            |  |

| Output 1 | Current       | 13             | 12                                                                                                                                                                                    |               |  |

|          | Current       | I3 Ret         |                                                                                                                                                                                       | 13            |  |

|          | Voltage       | V3             | 14                                                                                                                                                                                    |               |  |

|          | Voltage       | V3 Ret         |                                                                                                                                                                                       | 15            |  |

|          | 24V dc Common | 1794-          | 1794-TB3 — 16 thru 33 <sup>(1)</sup> 1794-TB3T, -TB3TS — 17, 18, 33 1794-TBN, -TBNF — 16 and 33  1794-TB3 — 34 thru 51 1794-TB3T, -TB3TS — 34, 35, 50, 51 1794-TBN, -TBNF — 34 and 51 |               |  |

|          | +24V dc power | 1794-TI        |                                                                                                                                                                                       |               |  |

|          |               |                |                                                                                                                                                                                       |               |  |

<sup>(1)</sup> Terminals 16 thru 33 are internally connected in the terminal base unit.

$<sup>^{(2)}</sup>$  Terminal 39 through 46 are chassis ground. Terminals 36, 37, 38 and 47, 48, 49 are used or cold junction compensation.

Total current draw through the terminal base unit is limited to 10A. Separate power connections to the terminal base unit may be necessary.

Figure 2.6

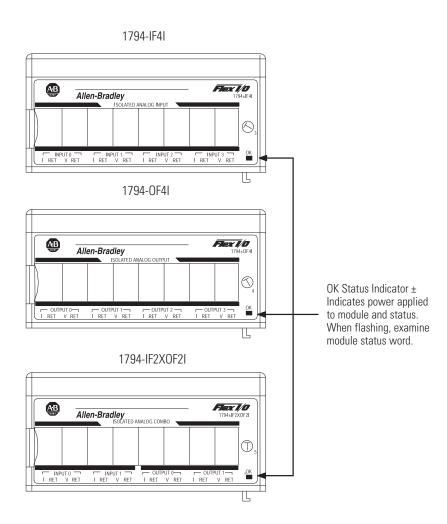

### **Module Indicators**

The analog modules have one status indicator that is on when power is applied to the module.

## **Chapter Summary**

In this chapter you learned how to install your input module in an existing programmable controller system and how to wire to the terminal base units.

## **Module Programming**

## **Chapter Objectives**

In this chapter, we tell you about:

- analog data format

- block transfer programming

- configuration rungs

- sample programs for the PLC-3 and PLC-5 processors

## Block Transfer Programming

Your module communicates with the processor through bidirectional block transfers. This is the sequential operation of both read and write block transfer instructions.

A configuration block transfer write (BTW) is initiated when the analog module is first powered up, and subsequently only when the programmer wants to enable or disable features of the module. The configuration BTW sets the bits which enable the programmable features of the module, such as filters and signal ranges, etc. Block transfer reads are performed to retrieve information from the module.

Block transfer read (BTR) programming moves status and data from the module to the processor's data table. The processor user program initiates the request to transfer data from the module to the processor. The transferred words contain module status, channel status and input data from the module.

The following sample programs are minimum programs; all rungs and conditioning must be included in your application program. You can disable BTRs, or add interlocks to prevent writes if desired. Do not eliminate any storage bits or interlocks included in the sample programs. If interlocks are removed, the program may not work properly.

Your program should monitor status bits, block transfer read and block transfer write activity.

## **Configuration Rungs**

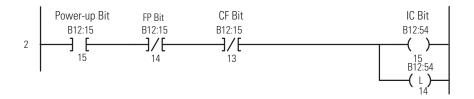

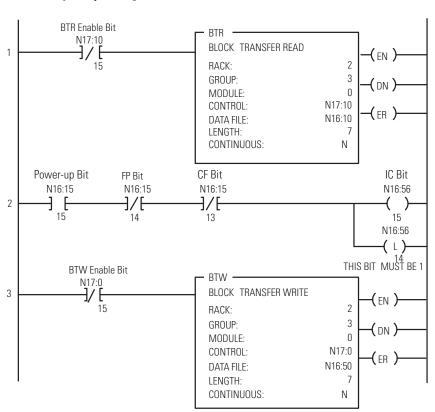

#### **Example Configuration Rungs**

It is necessary to toggle the IC bit<sup>(1)</sup> (initiate configuration) for the isolated analog modules to accept configuration data. Once the configuration data has been properly set up, the following rung will reconfigure the module (this example represents sizes for the 1794-IF4I module).

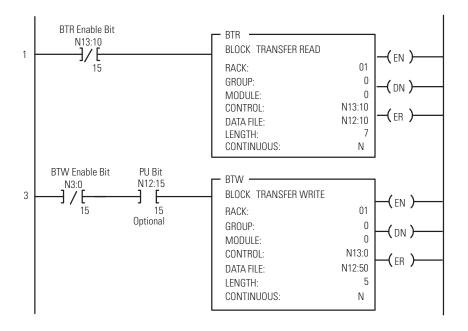

If there are rungs which already perform reads and writes to the module, no additional rungs are necessary. A simplified example of a BTR and BTW rung for an 1794-IF4I follow (the 1794-OF4I is read length 6, write length 7; the 1794-IF2XOF2I is read length 7, write length 7):

An XIC (-] [-] instruction of the Power Up bit (PU) can be inserted to allow BTWs only when the module requires configuration (PU = 1).

<sup>(1)</sup> For systems that do not require ladder program control of configuration, set the TR bit (bit 13) to 1. Refer to Chapter 1.

## Sample Programs for FLEX I/O Analog Modules

The following sample programs show you how to use your analog module efficiently when operating with a programmable controller. These programs show you how to:

- configure the module

- read data from the module

- update the module's output channels (if used)

With RSLogix5000, just read or write the tags provided. RSLogix will perform the transfer so an explicit block transfer is not required.

These programs illustrate the minimum programming required for communication to take place.

#### **PLC-3 Programming**

Block transfer instructions with the PLC-3 processor use one binary file in a data table section for module location and other related data. This is the block transfer control file. The block transfer data file stores data that you want transferred to your module (when programming a block transfer write) or from your module (when programming a block transfer read). The address of the block transfer data files are stored in the block transfer control file.

The same block transfer control file is used for both the read and write instructions for your module. A different block transfer control file is required for every module.

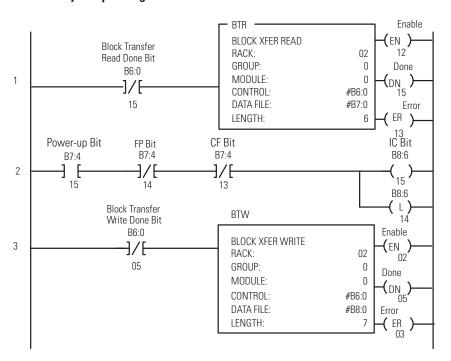

A sample program segment with block transfer instructions is shown in Figure 1.1, and described below.

Figure 1.1

PLC-3 Family Sample Program Structure for a 1794-IF4I Module

Figure 1.2

PLC-3 Family Sample Program Structure for a 1794-0F4I Module

#### Program Action

At power-up in RUN mode, or when the processor is switched from PROG to RUN, the user program enables a block transfer read.

This rung toggles the Initate Configuration bit from 0 to 1 to 0

Then it initiates a block transfer write to configure the module and send data values.

Thereafter, the program continuously performs read block transfers and write block transfers.

Note: You must create the data file for the block transfers before you enter the block transfer instructions.

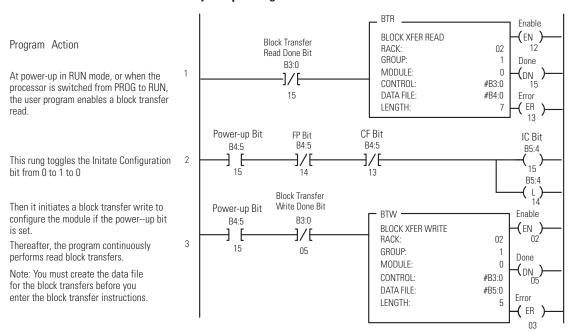

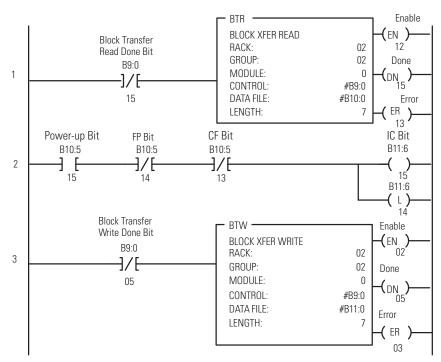

Figure 1.3 PLC-3 Family Sample Program Structure for a 1794-IF2XOF2I Module

#### Program Action

At power-up in RUN mode, or when the processor is switched from PROG to RUN, the user program enables a block transfer read.

This rung toggles the Initate Configuration bit from 0 to 1 to 0  $\,$

Then it initiates a block transfer write to configure the module and send data values

Thereafter, the program continuously performs read block transfers and write block transfers.

Note: You must create the data file for the block transfers before you enter the block transfer instructions.

### **PLC-5 Programming**

The PLC-5 program is very similar to the PLC-3 program with the following exceptions:

- block transfer enable bits are used instead of done bits as the conditions on each rung.

- separate block transfer control files are used for the block transfer instructions.

Figure 1.4 PLC-5 Family Sample Program Structure for the 1794-IF4I

#### Program Action

At power-up in RUN mode, or when the processor is switched from PROG to RUN, the user program enables a block transfer read.

This rung toggles the Initate Configuration bit from 0 to 1 to 0  $\,$

Then it initiates a block transfer write to configure the module if the power-up bit is set.

Thereafter, the program continuously performs read block transfers to configure the module.

The pushbutton allows the user to manually request a block transfer write.

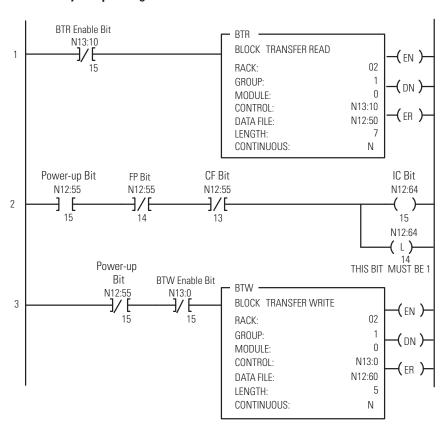

Figure 1.5 PLC-5 Family Sample Program Structure for the 1794-0F4I

CONTINUOUS:

Ν

Figure 1.6

PLC-5 Family Sample Program Structure for the 1794-IF2X0F2I

#### Program Action

At power-up in RUN mode, or when the processor is switched from PROG to RUN, the user program enables a block transfer read.

This rung toggles the Initate Configuration bit from 0 to 1 to 0  $\,$

Then it initiates a block transfer write to configure the module and send data values.

Thereafter, the program continuously performs read block transfers and write block transfers.

#### **PLC-2 Programming**

The 1794 analog I/O modules are not recommended for use with PLC-2 family programmable controllers due to the number of digits needed for high resolution.

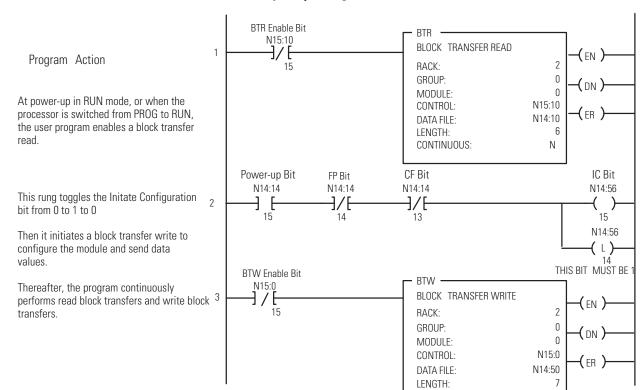

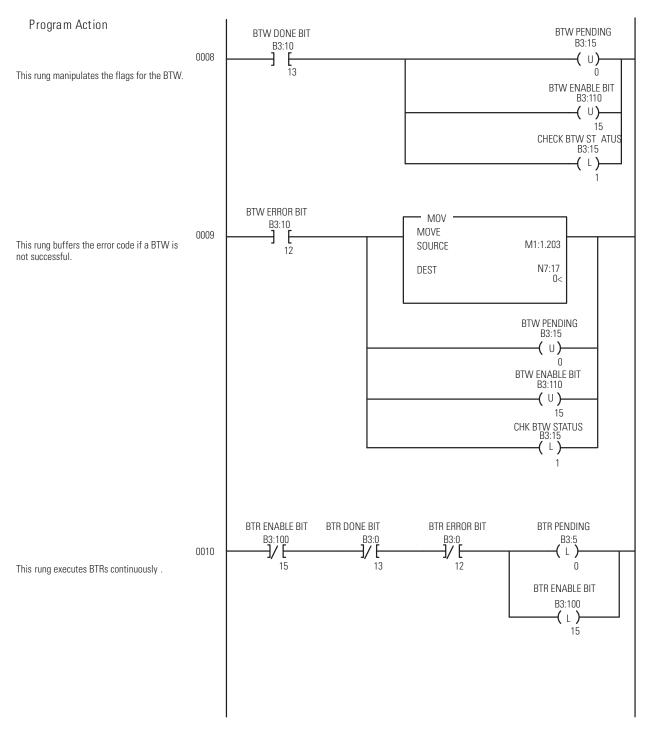

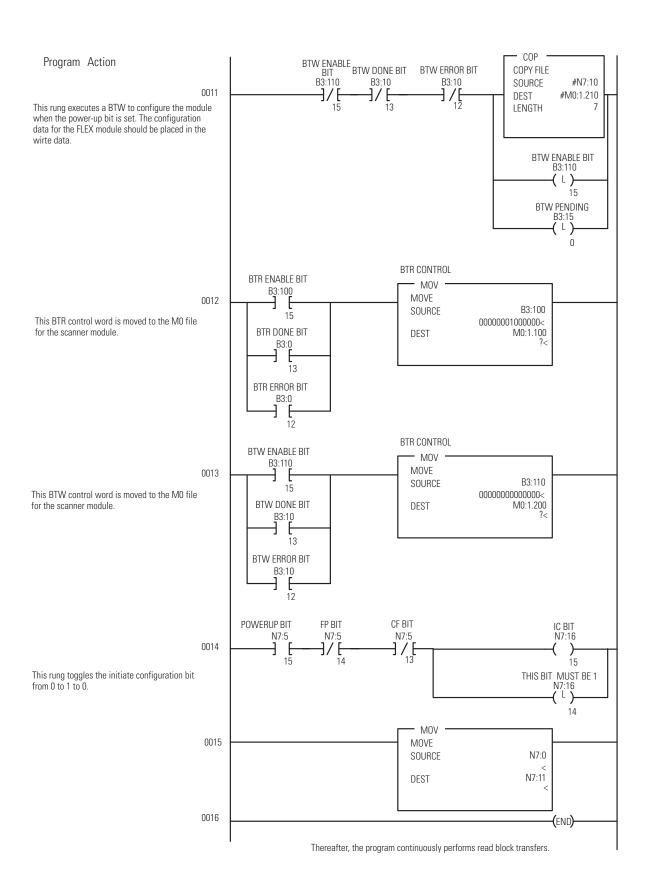

## **SLC-5 Programming**

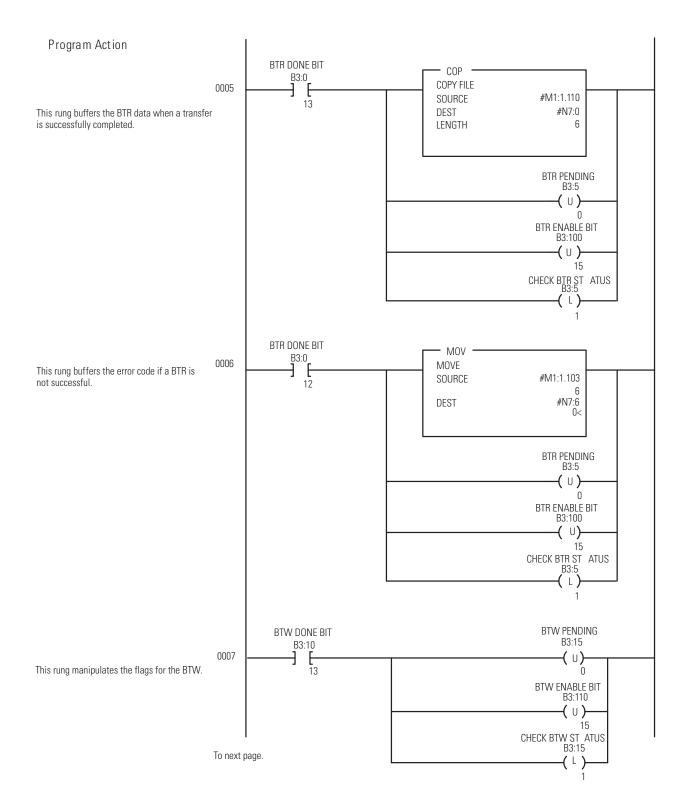

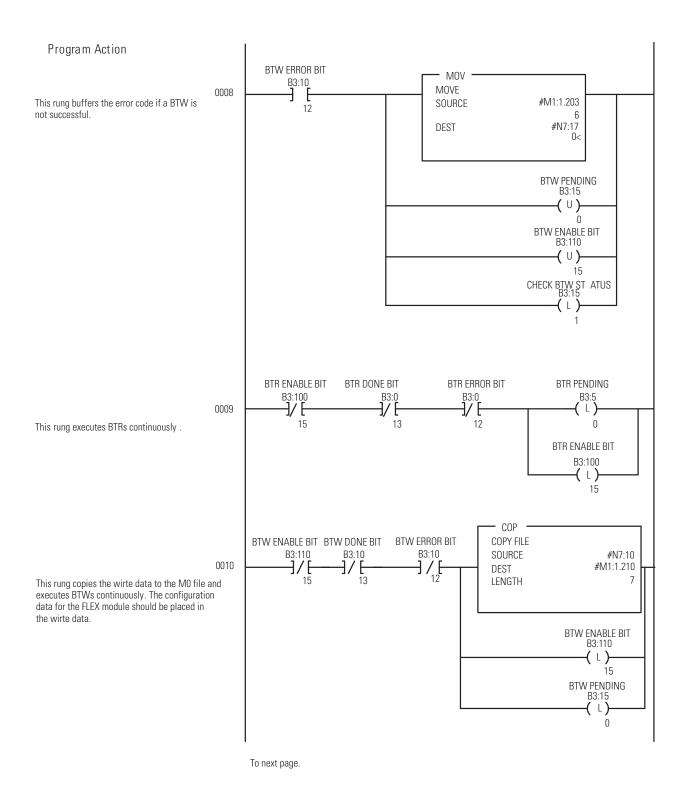

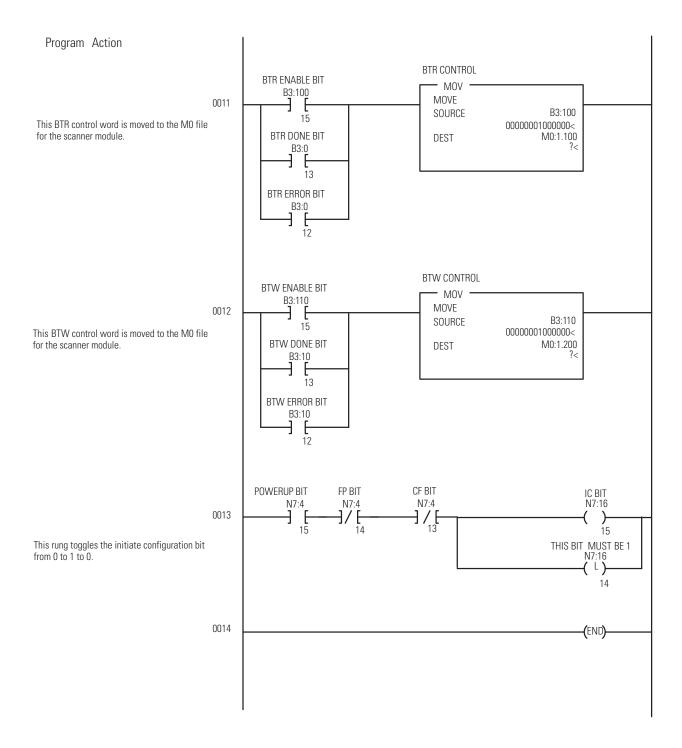

The SLC-5 programs (using the 1747-SN scanner) follow the same logic as the PLC-5 family programs in the previous examples. Differences occur in the implementation of block transfers due to the use of "M" files in the SLC system.

Configuration data for the FLEX I/O isolated analog modules and the 1747-SN scanner must be in place before executing the following programs. Chapter 4 contains information on the isolated analog module configurations.

For more information on using the 1747-SN scanner module and block transfer programming, refer to publication 1747-6.6, "Remote I/O Scanner User Manual."

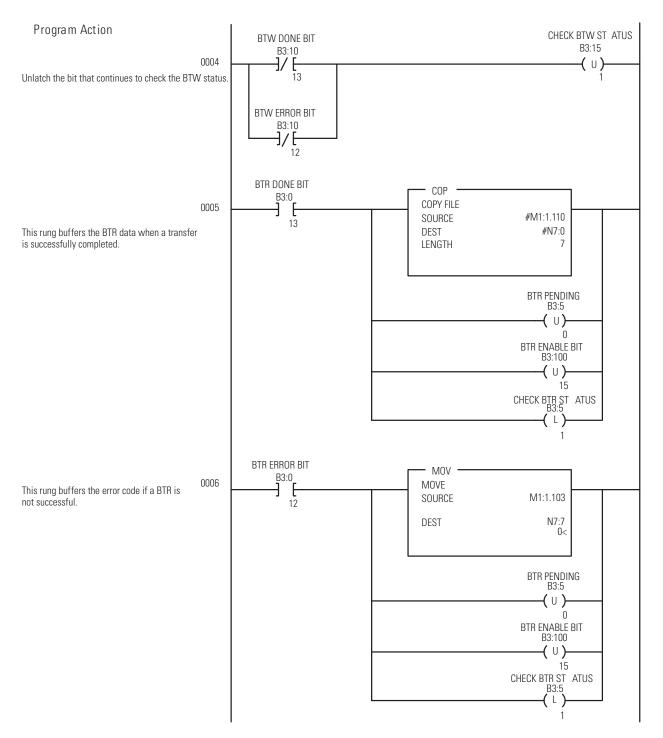

BTR\_CONTROL Program Action PowerUp Bit - COP COPY FILE 0000 #B3:100 SOURCE This rung configures the block transfer operation type, length, and RIO address at power-up. Bit B3:100/7 must be set to 1 to indicate a BTR and DEST #M0:1.100 LENGTH bit B3:110/7 must be 0 to indicate a BTW. BTW\_CONTROL - COP COPY FILE #B3:110 SOURCE DEST #M0:1.200 3 LENGTH BTR PENDING COP **COPY FILE** 0001 SOURCE #M1:1.100 BTR status is copied to the B3:0 area when a BTR DEST #B3:0 is in progress. LENGTH 4 CHECK BTR ST ATUS B3:5 CHECK BTR ST ATUS BTR DONE BIT B3:5 B3:0 (∪) 0002 Unlatch the bit that continues to check the BTR status. BTR ERROR BIT B3:0 BTW PENDING COP B3:15 COPY FILE #M1:1.200 SOURCE BTW status is copied to the B3:100 area when a 0 #B3:10 DEST BTW is in progress. LENGTH CHECK BTW ST ATUS B3:15 CHECK BTW ST ATUS BTW DONE BIT B3:15 B3:10 (∪) Unlatch the bit that continues to check the BTW status. BTW ERROR BIT To next page.

Figure 1.7 SLC Programming for the 1794-0F4I Isolated Analog Output Module

BTR\_CONTROL Program Action PowerUp Bit - COP **COPY FILE** 0000 #B3:100 SOURCE This rung configures the block transfer operation type, length, and RIO address at power-up. Bit B3:100/7 must be set to 1 to indicate a BTR and bit B3:110/7 must be 0 to indicate a BTW. DEST #M0:1.100 3 LENGTH BTW\_CONTROL - COP COPY FILE #B3:110 SOURCE #M0:1.200 DEST LENGTH BTR PENDING - COP B3:5 **COPY FILE** 0001 #M1:1.100 SOURCE BTR status is copied to the B3:0 area when a BTR #B3:0 DEST is in progress. 4 LENGTH CHECK BTR ST ATUS B3:5 CHECK BTR ST ATUS B3:5 BTR DONE BIT B3:0 (∪) 0002 Unlatch the bit that continues to check the BTR status. BTR ERROR BIT B3:0 12 BTW PENDING COP B3:15 COPY FILE 0003 SOURCE #M1:1.200 BTW status is copied to the B3:100 area when a 0 #B3:10 DEST BTW is in progress. LENGTH 4 CHECK BTW ST ATUS B3:15

To next page.

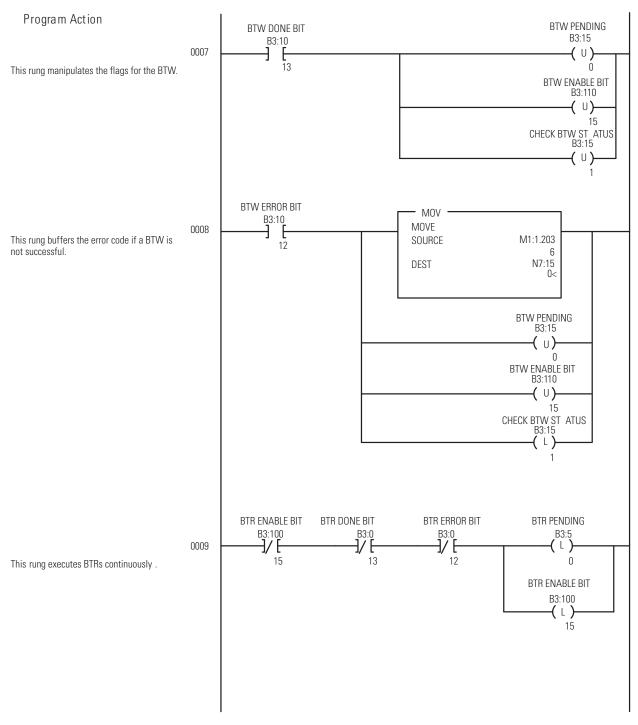

Figure 1.8

SLC Programming for the 1794-IF4I Isolated Analog Input Module

To next page.

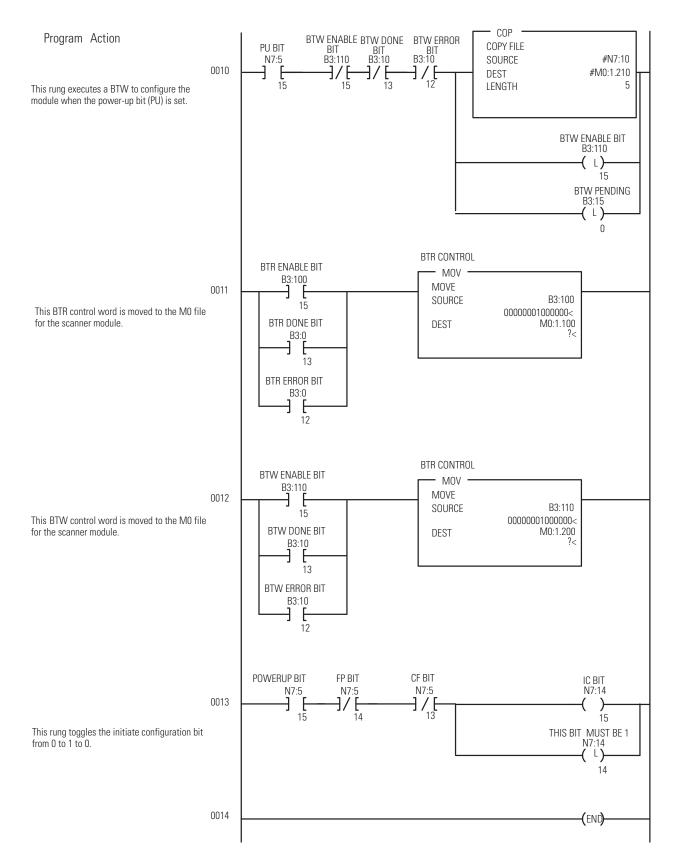

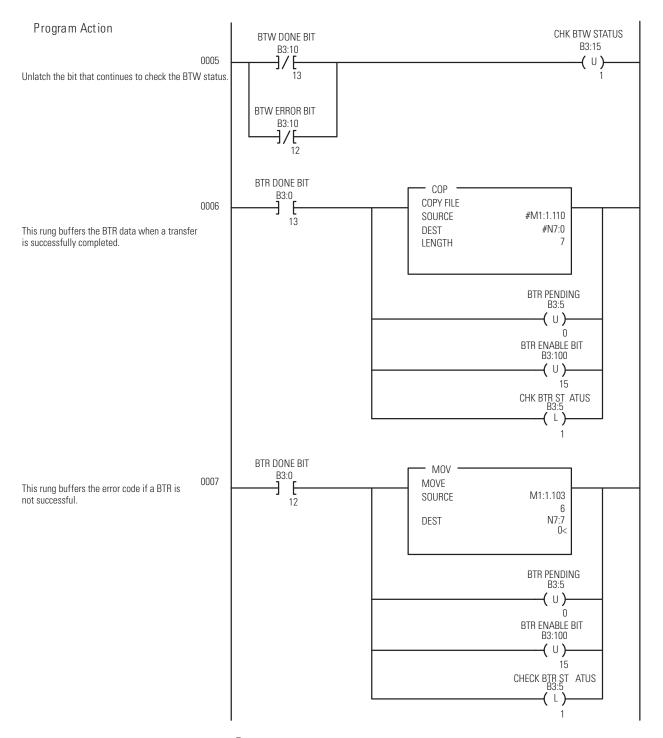

Program Action BTR\_CONTROL PowerUp Bit - COP COPY FILE **–** 15 0000 #B3:100 SOURCE This rung configures the block transfer operation type, length, and RIO address at power-up. Bit #M0:1.100 DEST 3 LENGTH B3:100/7 must be set to 1 to indicate a BTR and bit B3:110/7 must be 0 to indicate a BTW. BTW\_CONTROL - COP **COPY FILE** SOURCE #B3:110 #M0:1.200 DEST 3 LENGTH BTR PENDING - COP B3:5 **COPY FILE** 0001 SOURCE #M1:1.100 BTR status is copied to the B3:0 area when a BTR DEST #B3:0 is in progress. LENGTH 4 CHK BTR ST ATUS B3:5 CHK BTR ST ATUS BTR DONE BIT B3:5 B3:0 (U) 0002 Unlatch the bit that continues to check the BTR status. BTR ERROR BIT B3:0 BTW PENDING COP B3:5 **COPY FILE** 0003 #M1:1.100 SOURCE BTW status is copied to the B3:100 area when a DEST #B3:0 BTW is in progress. LENGTH 4 CHK BTW STATUS B3:5 BTW PENDING COP **COPY FILE** 0004 SOURCE #M1:1.200 #B3:10 DEST LENGTH 4 CHK BTW STATUS B3:15 To next page.

Figure 1.9 SLC Programming for the 1794-IF2XOF2I Isolated Analog Input/Output Module

## **Chapter Summary**

In this chapter, you learned how to program your programmable controller. You were given sample programs for your PLC-3 and PLC-5 family processors.

# Writing Configuration to and Reading Status from Your Module with a Remote I/O Adapter

## **Chapter Objectives**

In this chapter, we tell you about:

- configuring your module's features

- entering your data

- reading data from your module

- read block format

## Configuring Your Analog Module

Because of the many analog devices available and the wide variety of possible configurations, you must configure your module to conform to the analog device and specific application that you have chosen. The module is configured using a group of data table words that are transferred to the module using a block transfer write instruction.

The software configurable features available are:

- input/output range selection

- data type (two's complement, two's complement percent, binary and offset binary)

PLC-5 family programmable controllers that use 6200 software programming tools can take advantage of the IOCONFIG utility to configure these modules. IOCONFIG uses menu-based screens for configuration without having to set individual bits in particular locations. Refer to your 6200 software literature for details.

TIP

RSLogix family programmable controllers that use RSLogix software programming tools can take advantage of the configuration GUI to configure these modules.

## **Range Selection**

Individual input channels are configurable to operate with the following voltage or current ranges:

Table 4.1 Range Selection

| Input channel Co   | nfiguration                |                              |

|--------------------|----------------------------|------------------------------|

| Input Values       | Data Format                | % Underrange/<br>% Overrange |

| Channel not config | ured                       |                              |

| 4–20mA             | signed 2's complement      | 4% Under; 4% Over            |

| ±10V               | signed 2's complement      | 2% Under, 2% Over            |

| ±5V                | signed 2's complement      | 4% Under, 4% Over            |

| 0-20mA             | signed 2's complement %    | 0% Under, 4% Over            |

| 4-20mA             | signed 2's complement %    | 4% Under, 4% Over            |

| 0-10V              | signed 2's complement %    | 0% Under, 2% Over            |

| ±10V               | signed 2's complement %    | 2% Under, 2% Over            |

| 0-20mA             | binary                     | 0% Under, 4% Over            |

| 0-10V              | binary                     | 0% Under, 2% Over            |

| 0-5V               | binary                     | 0% Under, 4% Over            |

| ±20mA              | offset binary, 8000H = 0mA | 4% Under, 4% Over            |

| 4–20mA             | offset binary, 8000H = 4mA | 4% Under, 4% Over            |

| ±10V               | offset binary, 8000H = 0V  | 2% Under, 2% Over            |

| ±5V                | offset binary, 8000H = 0V  | 4% Under, 4% Over            |

You can select individual channel ranges using the designated words of the write block transfer instruction. Refer to the Bit/Word description for your particular module for word and bit numbers.

#### **Safe State Selection**

You can select the analog values that your output module will maintain in the event of a network communication error. When the enable bit is cleared by a communication error, the analog outputs will automatically switch to the values set in the safe state analog words as defined by the safe state source bits. This allows you to select a reset to 0V/0mA, or hold the outputs at their last state when using the remote I/O adapter on remote I/O. Additionally, safe state values can be setup using ControlNet, DeviceNet or other network adapter.

#### **Data Format**

The input/output data exchanged between the module and the adapter is available in two's complement, two's complement percent, binary and offset binary (refer to the range selection table above).

## **Real Time Sampling**

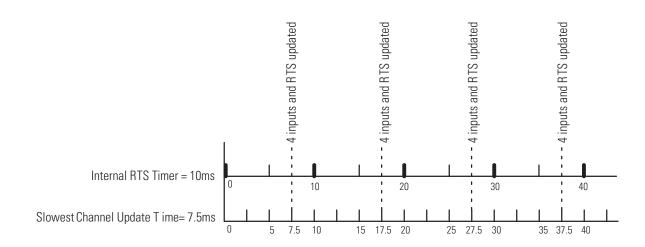

Real time sampling (RTS) provides data gathered at precise intervals for use by the processor. You set a word in the block transfer write data file to enable RTS.

The real time sample programmed interval is the time at which updated information will be supplied to the processor. When set to "0" the module will default to each channel's fastest update rate, which is dependent on the nominal range of the input and the filter setting set to "no low pass."

When the IT interrupt toggle bit is set (1), interleaving of module interrupts occurs, ensuring exchange of critical data when channels are configured for their fastest update times. RTSI and "no low pass filter" must be 0 in order for the module to recognize this feature. This groups data update rates for all channels to the slowest configuration setting of any of the channels. In addition, channel update rates for all channels with a 7.5ms update rate are reduced to 5.0ms. When reset (0), real time sampling and filter features are enabled.

Table 4.2 Real Time Sample Interval

| Configuration | Nominal Range | Channel<br>Update Rate<br>(RTS = 0) <sup>(1)</sup> | Channel Update Rate (RTS and Filter = 0) <sup>(1)</sup> and IT = 1 |

|---------------|---------------|----------------------------------------------------|--------------------------------------------------------------------|

| 1             | 4-20mA        | 7.5ms                                              | 5.0ms                                                              |

| 2             | ±10V          | 2.5ms                                              | 2.5ms                                                              |

| 3             | ±5V           | 2.5ms                                              | 2.5ms                                                              |

| 4             | 0-20mA        | 7.5ms                                              | 5.0ms                                                              |

| 5             | 4-20mA        | 7.5ms                                              | 5.0ms                                                              |

| 6             | 0-10V         | 5.0ms                                              | 5.0ms                                                              |

| 7             | ±10V          | 5.0ms                                              | 5.0ms                                                              |

| 8             | 0-20mA        | 2.5ms                                              | 2.5ms                                                              |

| 9             | 4-20mA        | 7.5ms                                              | 5.0ms                                                              |

| А             | 010V          | 2.5ms                                              | 2.5ms                                                              |

| В             | 0-5V          | 2.5ms                                              | 2.5ms                                                              |

| С             | ±20mA         | 2.5ms                                              | 2.5ms                                                              |

| D             | 4-20mA        | 7.5ms                                              | 5.0ms                                                              |

| Е             | ±10V          | 2.5ms                                              | 2.5ms                                                              |

| F             | ±5V           | 2.5ms                                              | 2.5ms                                                              |

<sup>(1)</sup> Channel filter set to "no low pass."

The real time sample interval can be set from 0 to 30s, in increments of 5ms. Set the real time sample interval in binary using 15 bits in the block transfer write word.

| Word/Dec. Bit  | 15 | 14 | 13 | 12 | 11 | 10                                   | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------------|----|----|----|----|----|--------------------------------------|----|----|----|----|----|----|----|----|----|----|

| Word/Octal Bit | 17 | 16 | 15 | 14 | 13 | 12                                   | 11 | 10 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| Word 3         | 0  |    |    |    |    | Real Time Sample Programmed Interval |    |    |    |    |    |    |    |    |    |    |

The individual channel update times determines how fast you can get new information collectively from the module. The module gathers the data from each input and makes it available to the processor. For example, if channel 0 is 2.5ms, channel 1 is 5.0ms, and channel 2 is 7.5ms, and RTS = 0, each channel will be updated at its stated rate. If RTS is set to 5ms, only channels 0 and 1 are fast enough to be included in the real time sample. In order to include channel 2 in your synchronous sample, you must set the RTS to 10ms minimum. Your updated information will be accurate for all inputs/outputs as viewed at the last update before the time of your request.

ATTENTION

Do not set your real time sample interval less than the slowest channel's update time.

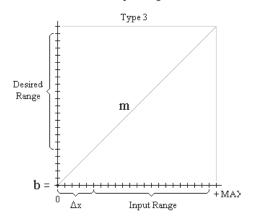

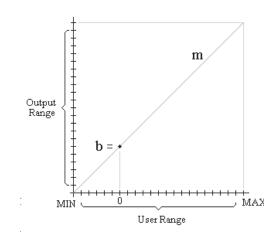

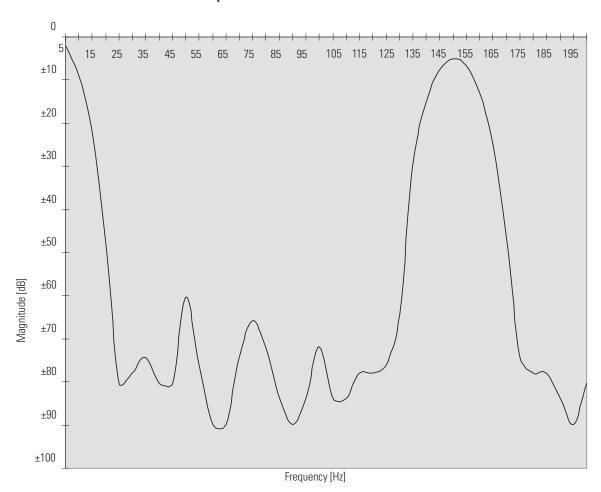

## **Input Filtering**

The input modules have selectable input filtering built into the A/D converter. The filter attenuates the input signal beginning at the specified frequency. You can select from 150, 300, 600, and 1200Hz with low pass filters of none, 100ms, 500ms or 1000ms. Each channel filter

can be set individually. Select the filter based on your system requirements.

| A/D Conversion Rate | Low Pass Filter |

|---------------------|-----------------|

| 1200Hz              | No low pass     |

| 1200Hz              | 100ms low pass  |

| 1200Hz              | 500ms low pass  |

| 1200Hz              | 1000ms low pass |

| 600Hz               | No low pass     |

| 600Hz               | 100ms low pass  |

| 600Hz               | 500ms low pass  |

| 600Hz               | 1000ms low pass |

| 300Hz               | No low pass     |

| 300Hz               | 100ms low pass  |

| 300Hz               | 500ms low pass  |

| 300Hz               | 1000ms low pass |

| 150Hz               | No low pass     |

| 150Hz               | 100ms low pass  |

| 150Hz               | 500ms low pass  |

| 150Hz               | 1000ms low pass |

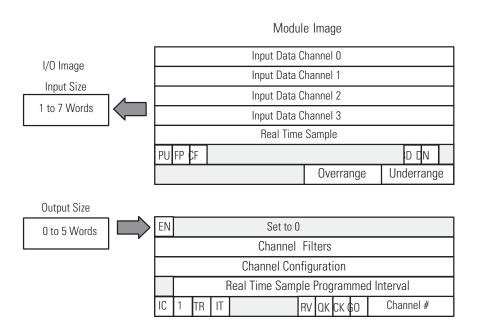

## Reading Data From Your Module

Read programming moves status and data from the module to the processor's data table. The processor's user program initiates the request to transfer data from the input module (or combination module) to the processor.

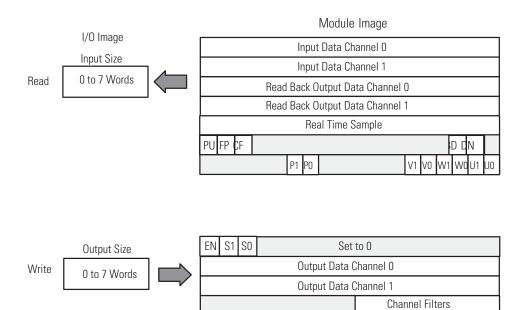

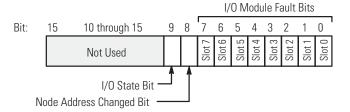

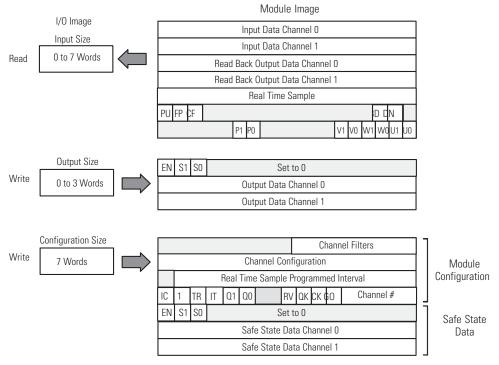

## Mapping Data for the Analog Modules

The following read and write words and bit/word descriptions describe the information written to and read from the analog modules. Each word is composed of 16 bits.

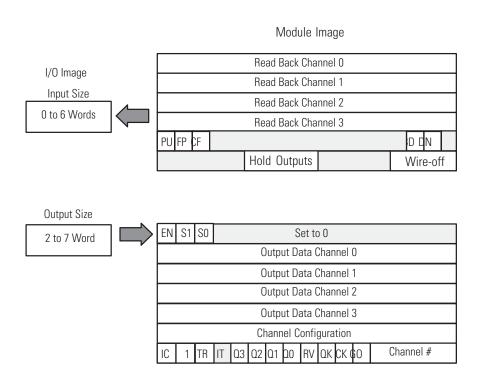

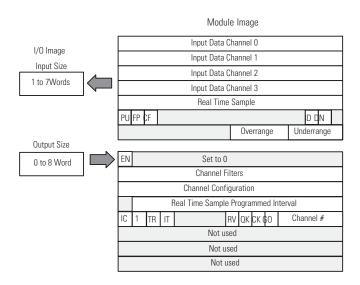

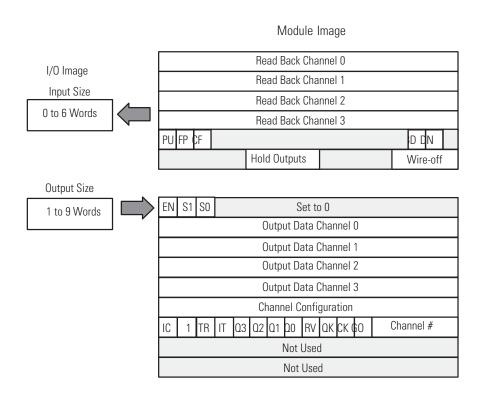

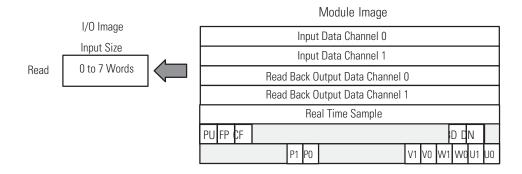

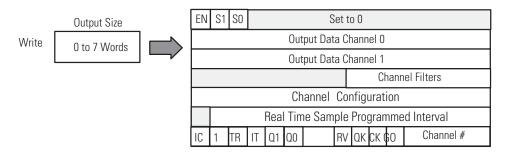

#### 8 Input Analog Module (Cat. No. 1794-IF4I)

Table 4.3 Analog Input Module (1794-IF4I) Read

| Word/Dec. Bit  | 15     | 14                     | 13   | 12     | 11 | 10       | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------------|--------|------------------------|------|--------|----|----------|----|----|----|----|----|----|----|----|----|----|

| Word/Octal Bit | 17     | 16                     | 15   | 14     | 13 | 12       | 11 | 10 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

| Read Word 0    | Analo  | nalog Value Channel O  |      |        |    |          |    |    |    |    |    |    |    |    |    |    |

| Word 1         | Analo  | nalog Value Channel 1  |      |        |    |          |    |    |    |    |    |    |    |    |    |    |

| Word 2         | Analo  | Analog Value Channel 2 |      |        |    |          |    |    |    |    |    |    |    |    |    |    |

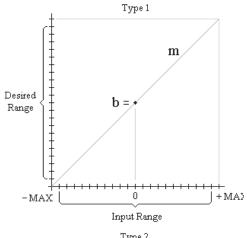

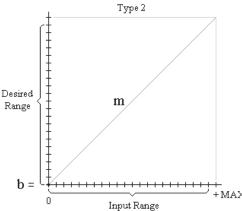

| Word 3         | Analo  | g Value                | Cha  | nnel 3 |    |          |    |    |    |    |    |    |    |    |    |    |